(peripheral component interconnect express)是一種高速串列計算機擴展匯流排標準,它原來的名稱為“3gio”,是由在2001年提出的,旨在替代舊的pci,pci-x和agp匯流排標準。pcie屬於高速串列點對點雙通道高頻寬傳輸,所連線的設備分配獨享通道頻寬,不共享匯流排頻寬,主要支持主動電源管理,錯誤報告,端對端的可靠性傳輸,熱插拔以及服務質量()等功能。pcie交由(pci特殊興趣組織)認證發布後才改名為“pci-express”,簡稱“pci-e”。它的主要優勢就是數據傳輸速率高,目前最高的16x 2.0版本可達到10gb/s,而且還有相當大的發展潛力。pci express也有多種規格,從pci express x1到pci express x32,能滿足將來一定時間內出現的低速設備和高速設備的需求。最新的接口是pcie 3.0接口,其比特率為8gbps,約為上一代產品頻寬的兩倍,並且包含發射器和接收器均衡、pll改善以及時鐘數據恢復等一系列重要的新功能,用以改善數據傳輸和數據保護性能。pcie快閃記憶體卡的供應商包括:intel、、lsi、、三星(計畫中)、、stec、supertalent和(計畫中)等,而針對海量的數據增長使得用戶對規模更大、可擴展性更強的系統所套用,pcie 3.0技術的加入最新的lsi megaraid控制器及hba產品的出色性能,就可以實現更大的系統設計靈活性。截止2019年1月份,當前主流主機板均支持pcie 3.0

基本介紹

- 中文名:高速串列計算機擴展匯流排標準

- 外文名:pcie

- 提出公司:

- 提出時間:2001年

- 含義:最新的和接口標準

pcie意義,是pci的更高發展,2.0升級部分,角色定位,pcie規格,結構,互連,通道,串列匯流排,形式參數,pcie標準,引腳排列,電源,pci express迷你卡,衍生形式,歷史版本,pcie 1.0a,pcie 1.1,pcie 2.0,pcie 2.1,pcie 3.0,pcie 3.1,pcie 4.0,pci-e sd 7.0,擴展和未來方向,硬體協定摘要,物理層,數據鏈路層,事務層,套用,外部gpu,存儲設備,群集互連,pci-e 3.0,pci-e 3.0 要求,pci express 鏈路,pci express fabric拓撲,pci-e 4.0,競爭協定,

pcie意義

是pci的更高發展

pcie比以前的標準有許多改進,包括更高的最大系統匯流排吞吐量,更低的i/o引腳數量和更小的物理尺寸,更好的匯流排設備性能縮放,更詳細的錯誤檢測和報告機制(高級錯誤報告,aer)和本機熱插拔功能。 pcie標準的更新版本為i/o虛擬化提供了硬體支持。

pci express電接口也用於各種其他標準,最值得注意的是作為筆記本電腦擴展卡接口的expresscard以及作為計算機存儲接口的sata express。

pci express 2.0規範的主要在數據傳輸速度上做出了重大升級,即從以前的2.5gt/s匯流排頻率翻倍至5gt/s,這也就是說以前pci express 2.0 x16接口能夠翻番達到驚人的8gb/s(1gb/s=8gbps)。

目前最新的版本為pci-e 3.0,是生產中可用於主流個人電腦的擴展卡的最新標準。也有還未退市的pci-e(即1.0版)。而在2009年的第二季度發布的amd rd890將率先支持pci-e 3.0版本。2.0比1.0提高一倍,而3.0比2.0版頻寬又提升一倍,為5ghz x 4。

2.0升級部分

1、重點是pci express匯流排頻率提升:每條串列線路的數據傳輸率從2.5gbps翻番至5gbps,也隨之翻倍。

2、可更好地支持未來高端顯示卡,即使功耗達到225w或者300w也只需pci express單獨供電即可。

3、新增“輸入輸出虛擬化”(iov)技術,可以讓多台虛擬機共享網卡等pci設備。

4、pci-e線纜子規範可讓pci設備通過標準化銅纜線接入計算機,而且每條線路的速度都能達到2.5gbps,適用於為高端伺服器加入多塊網卡作為輸入輸出擴展模組等場合。

5、最後是代號“geneseo”的長期規劃。該技術與intel、ibm等業界巨頭合作開發,可讓圖形處理單元、加密處理單元等更好地與緊密相連。

6、對速度和鏈路寬度管理、以及活動狀態電源管理(aspm)進行相關改進。

角色定位

emc公司最近更新的快取策略鞏固了固態pci express在伺服器中的地位,並將和其他it廠商一起為提升企業數據存儲的效率扮演重要的角色。

但是pci express flash是否從根本上影響了整個行業以及是否對典型的數據中心具有吸引力仍然值得討論。技術具有兩面性,it企業對新挑戰還是抱有謹慎的態度。但是沒人會否認pcie不論是在快取還是在主存里提升的優越性能。

pcie的主要優勢在於其減少延遲的能力。pcie設備和pcie匯流排直接相連,使快取和數據更接近cpu。他們消除了傳統存儲協定的開銷,並且emc認為在合適的條件下能實現遠遠優於從08年開始銷售的串列scsi和sata的固態硬碟ssd的性能。

pcie規格

傳輸通道數 | 腳pin總數 | 主接口區pin數 | 總 長 度 | 主接口區 長度 |

1 | 36 | 14 | 25 mm | 7.65 mm |

4 | 64 | 42 | 39 mm | 21.65 mm |

8 | 98 | 76 | 56 mm | 38.65 mm |

16 | 164 | 142 | 89 mm | 71.65 mm |

規格 | 匯流排寬度 | 工作時脈 | 傳輸速率 |

pci-e x1 | 8 位 | 2.5 ghz | 512 mib/s |

pci-e x2 | 8 位 | 2.5 ghz | 1.0 gib/s |

pci-e x4 | 8 位 | 2.5 ghz | 2.0 gib/s |

pci-e x8 | 8 位 | 2.5 ghz | 4.0 gib/s |

pci-e x16 | 8 位 | 2.5 ghz | 8.0 gib/s |

結構

在概念上,匯流排是較舊的/ pci-x匯流排的高速串列替換。pci express匯流排與舊pci之間的主要區別之一是匯流排拓撲。 pci使用共享並行匯流排架構,其中pci主機和所有設備共享一組通用的地址,數據和控制線。 相比之下,pci express基於點到點拓撲,單獨的串列鏈路將每個設備連線到根系統(主機)。 由於其共享匯流排拓撲,可以對單個方向上的pci匯流排進行仲裁(在多個主機的情況下),並且一次限制為一個主機。 此外,舊的pci時鐘方案將匯流排時鐘限制在匯流排上最慢的外設(不管匯流排事務中涉及的設備如何)。 相比之下,pci express匯流排鏈路支持任何兩個端點之間的全雙工通信,同時跨多個端點的並發訪問沒有固有的限制。

在匯流排協定方面,pci express通信封裝在數據包中。打包和解包數據和狀態訊息流量的工作由pci express連線埠的事務層處理,電信號和匯流排協定的根本差異需要使用不同的機械外形尺寸和擴展連線器(因此,需要新的主機板和新的適配器板); pci插槽和pci express插槽不可互換。在軟體級別,pci express保留與pci的向後兼容性; 傳統的pci系統軟體可以檢測和配置較新的pci express設備,而無需顯式支持pci express標準,但是新的pci express功能無法訪問。兩個設備之間的pci express鏈路可以由1個到32個通道組成。 在多通道鏈路中,分組數據在通道上條帶化,並且峰值數據吞吐量與整個鏈路寬度成比例。通道計數在設備初始化期間自動協商,並且可以被任一端點限制。例如,單通道pci express(×1)卡可以插入多通道插槽(×4,×8等),初始化周期自動協商最高相互支持的通道數。該連結可以動態地自動配置自己,以便使用較少的通道,在存在不良或不可靠的通道的情況下提供故障容限。pci express標準定義了多個寬度的插槽和連線器:×1,×4,×8,×12,×16和×32。這允許pci express匯流排服務於不需要高吞吐量的成本敏感型套用,以及諸如3d圖形,網路(萬兆乙太網或多連線埠千兆位乙太網)和企業級存儲(sas或光纖通道)等關鍵性能的套用。

作為參考,使用四路(×4)的pci-x(133mhz 64位)設備和pci express 1.0設備具有大致相同的峰值單向傳輸速率為1064mb / s。 在多個設備同時傳輸數據的情況下,或者與pci express外設的通信是雙向的情況下,pci express匯流排具有比pci-x匯流排更好的性能。

互連

pci express設備通過稱為互連或鏈路的邏輯連線進行通信。鏈路是兩個pci express連線埠之間的點對點通信通道,允許它們傳送和接收普通pci請求(配置,i / o或存儲器讀/寫)和中斷(intx,msi或msi-x) 。 在物理層面上,一條鏈路由一條或多條通道組成。低速外設(例如802.11 wi-fi卡)使用單通道(×1)鏈路,而圖形適配器通常使用更寬更快的16通道鏈路。

通道

通道由兩個差分信號對組成,一對用於接收數據,另一對用於傳送。 因此,每個通道由四條線或信號跡線組成。在概念上,每條通道用作全雙工位元組流,在鏈路端點之間的兩個方向同時傳輸8位“位元組”格式的數據包。物理pci express鏈路可能包含1個到32個通道,更精確地包括1,2,4,8,12,16或32個通道。通道計數用“×”前綴( 例如“×8”表示八通道卡或插槽),×16是常用的最大尺寸。

串列匯流排

由於後者的固有限制,包括半雙工操作,超量信號計數以及由於定時偏移引起的固有的較低頻寬,因此,傳統的並行匯流排選擇了綁定串列匯流排架構。定時偏移來自在不同長度的導線,潛在不同的印刷電路板(pcb)層和可能不同的信號速度下行進的並行接口內的分離的電信號。儘管作為單個字同時傳輸,並行接口上的信號具有不同的行進持續時間,並在不同時間到達其目的地。當接口時鐘周期短於信號到達之間的最大時間差時,就不可能恢復傳輸的字。由於並行匯流排上的定時偏移量可能達到幾納秒,因此所產生的頻寬限制在幾百兆赫的範圍內。

串列接口不會出現定時偏移,因為每個通道中每個方向只有一個差分信號,並且由於時鐘信息嵌入在串列信號本身中,所以沒有外部時鐘信號。因此,串列信號的典型頻寬限制在幾千兆赫範圍內。 pci express是串列互連替代並行匯流排的一般趨勢的一個例子;其他示例包括serial ata(sata),usb,serial attached scsi(sas),firewire(ieee 1394)和rapidio。在數字視頻中,常用的例子有dvi,hdmi和displayport。

多通道串列設計增加了靈活性,其能夠為較慢的設備分配較少的通道。

形式參數

pcie標準

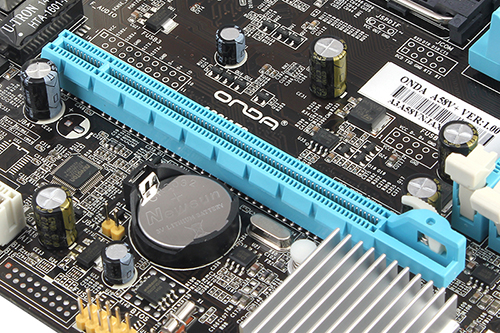

pci express卡適合其物理尺寸或更大的插槽(使用×16作為最大的),但可能不適合更小的pci express插槽;例如,×16卡可能不適合×4或×8插槽。一些插槽使用開放式插座來允許物理上更長的卡,並協商最佳的電子和邏輯連線。350px-pciexpress

實際連線到插槽的通道數量也可能少於物理槽大小所支持的數量。一個例子是一個×16插槽可以運行×1、×2、×4、×8、×16的卡,當運行×4卡時只提供4條通道。其規格可以讀為“×16(×4模式)”,而“×size @×速度”符號(“×16 @×4”)也是常見的。優點是這樣的插槽可以容納更大範圍的pci express卡,而不需要主機板硬體來支持全傳輸速率。

卡本身設計和製造各種尺寸。例如,以pci express卡形式出現的固態驅動器(ssd)通常使用hhhl(半高,半長)和fhhl(全高,半長)來描述卡的物理尺寸。(右圖中上面四個為pcie插槽,最下面一個為pci插槽)

引腳排列

下表列出了pci express卡上邊緣連線器每側的導線。 印刷電路板(pcb)的焊接側為a側,元件側為b側。prsnt1#和prsnt2#引腳必須稍短於其他引腳,以確保熱插拔卡完全插入。wake#引腳使用全電壓喚醒計算機,但必須從備用電源拉高以指示卡是可以喚醒。

pcie 連線器引腳(×1、×4、×8和×16變體) | ||||||||

引腳 | b側 | a側 | 描述 | 引腳 | b側 | a側 | 描述 | |

1 | 12v | prsnt1# | 必須連線到最遠的prsnt2 # | 50 | hsop(8) | 保留 | 通道8傳輸數據, 和- | |

2 | 12v | 12v | 主電源引腳 | 51 | hson(8) | 地面 | ||

3 | 12v | 12v | 52 | 地面 | hsip(8) | 通道8接收數據, 和- | ||

4 | 地面 | 地面 | 53 | 地面 | hsin(8) | |||

5 | smclk | tck | 和連線埠引腳 | 54 | hsop(9) | 地面 | 通道9傳輸數據, 和- | |

6 | smdat | tdi | 55 | hson(9) | 地面 | |||

7 | 地面 | tdo | 56 | 地面 | hsip(9) | 通道9接收數據, 和- | ||

8 | 3.3v | tms | 57 | 地面 | hsin(9) | |||

9 | trst# | 3.3v | 58 | hsop(10) | 地面 | 通道10傳輸數據, 和- | ||

10 | 3.3v aux | 3.3v | 59 | hson(10) | 地面 | |||

11 | 激活# | 復位# | 連結激活;復位 | 60 | 地面 | hsip(10) | 通道10接收數據, 和- | |

關鍵的缺口 | 61 | 地面 | hsin(10) | |||||

12 | clkreq# | 地面 | 請求運行時鐘 | 62 | hsop(11) | 地面 | 通道11傳輸數據, 和- | |

13 | 地面 | refclk | 參考時鐘差分對 | 63 | hson(11) | 地面 | ||

14 | hsop(0) | refclk− | 通道0傳輸數據, 和- | 64 | 地面 | hsip(11) | 通道11接收數據, 和- | |

15 | hson(0) | 地面 | 65 | 地面 | hsin(11) | |||

16 | 地面 | hsip(0) | 通道0接收數據, 和- | 66 | hsop(12) | 地面 | 通道12傳輸數據, 和- | |

17 | prsnt2# | hsin(0) | 67 | hson(12) | 地面 | |||

18 | 地面 | 地面 | 68 | 地面 | hsip(12) | 通道12接收數據, 和- | ||

pci express×1卡在引腳18處結束 | 69 | 地面 | hsin(12) | |||||

19 | hsop(1) | 保留 | 通道1傳輸數據, 和- | 70 | hsop(13) | 地面 | 通道13傳輸數據, 和- | |

20 | hson(1) | 地面 | 71 | hson(13) | 地面 | |||

21 | 地面 | hsip(1) | 通道1接收數據, 和- | 72 | 地面 | hsip(13) | 通道13接收數據, 和- | |

22 | 地面 | hsin(1) | 73 | 地面 | hsin(13) | |||

23 | hsop(2) | 地面 | 通道2傳輸數據, 和- | 74 | hsop(14) | 地面 | 通道14傳輸數據, 和- | |

24 | hson(2) | 地面 | 75 | hson(14) | 地面 | |||

25 | 地面 | hsip(2) | 通道2接收數據, 和- | 76 | 地面 | hsip(14) | 通道14接收數據, 和- | |

26 | 地面 | hsin(2) | 77 | 地面 | hsin(14) | |||

27 | hsop(3) | 地面 | 通道3傳輸數據, 和- | 78 | hsop(15) | 地面 | 通道15傳輸數據, 和- | |

28 | hson(3) | 地面 | 79 | hson(15) | 地面 | |||

29 | 地面 | hsip(3) | 通道3接收數據, 和- | 80 | 地面 | hsip(15) | 通道15接收數據, 和- | |

30 | 保留 | hsin(3) | 81 | prsnt2# | hsin(15) | |||

31 | prsnt2# | 地面 | 82 | 保留 | 地面 | |||

32 | 地面 | 保留 | ||||||

pci express×4卡在引腳32處結束 | ||||||||

33 | hsop(4) | 保留 | 通道4傳輸數據, 和- | |||||

34 | hson(4) | 地面 | ||||||

35 | 地面 | hsip(4) | 通道4接收數據, 和- | |||||

36 | 地面 | hsin(4) | ||||||

37 | hsop(5) | 地面 | 通道5傳輸數據, 和- | |||||

38 | hson(5) | 地面 | ||||||

39 | 地面 | hsip(5) | 通道5接收數據, 和- | |||||

40 | 地面 | hsin(5) | ||||||

41 | hsop(6) | 地面 | 通道6傳輸數據, 和- | |||||

42 | hson(6) | 地面 | ||||||

43 | 地面 | hsip(6) | 通道6接收數據, 和- | legend | ||||

44 | 地面 | hsin(6) | 接地引腳 | 零伏 | ||||

45 | hsop(7) | 地面 | 通道7傳輸數據, 和- | 電源引腳 | 為pcie卡供電 | |||

46 | hson(7) | 地面 | 卡到主機引腳 | 從卡到主機板的信號 | ||||

47 | 地面 | hsip(7) | 通道7接收數據, 和- | 主機到卡引腳 | 從主機板到卡的信號 | |||

48 | prsnt2# | hsin(7) | 可能拉低或由多張卡感應 | |||||

49 | 地面 | 地面 | 感應針 | 綁在一張卡上 | ||||

pci express×8卡在引腳49處結束 | 保留 | 目前不使用,請勿連結 | ||||||

電源

所有pci express卡在 3.3v(9.9w)可能消耗高達3a。它們可能消耗的 12v和總功率取決於卡的類型:

·×1卡在 12v(6w)和10w組合時限制為0.5a。

·×4和更寬的卡在 12v(25w)和25w組合時限制為2.1a。

·在初始化和軟體配置為“大功率設備”後,一個全尺寸×1卡可能會達到25 w限制。

·在初始化和軟體配置為“大功率設備”後,一個全尺寸×16顯示卡可以在 12v(66 w)和75 w組合後可能會達到5.5a限制。

可選連線器增加75 w(6引腳)或150 w(8引腳) 12 v電源,然後可以達到總共300 w(2×75 w 1×150 w)。一些卡使用兩個8針連線器,但這還沒有標準化,因此這種卡不能攜帶官方的pci express標誌。該配置允許總共375 w(1×75 w 2×150 w),並且可能會通過pci-sig與pci express 4.0標準進行標準化。 8針pci express連線器可能與eps12v連線器混淆,eps12v連線器主要用於為smp和多核系統供電。

pci express迷你卡

基於pci express的pci express迷你卡(也稱為mini pci express,mini pcie,mini pci-e,mpcie和pem)是mini pci外形尺寸的替代品。 它是由pci-sig開發的。 主機設備支持pci express和usb 2.0連線,每個卡都可以使用任一標準。 大多數筆記本電腦2005年之後構建使用pci express進行擴展卡; 然而,截至2015年,許多供應商正在為此目的使用較新的m.2外形尺寸。

由於尺寸不同,pci express迷你卡與標準全尺寸pci express插槽不兼容; 然而,存在允許它們在全尺寸插槽中使用的被動適配器。

1、物理尺寸

pci express迷你卡的尺寸為全迷你卡的30×50.95毫米(寬度×長度)。 有一個52針邊緣連線器,由0.8 mm間距的兩個交錯行組成。 每行有八個觸點,一個間隙相當於四個觸點,然後另外18個觸點。 板的厚度為1.0毫米,不包括部件。 還規定了“半迷你卡”(有時簡稱為hmc),其大約一半的物理長度為26.8毫米。

2、電接口

pci express迷你卡邊緣連線器提供多種連線和匯流排:

·pci express×1(帶smbus)

·usb 2.0

·用於診斷計算機機箱上無線網路led(即wi-fi)狀態的電線

·用於gsm和wcdma套用的sim卡(規格為uim信號)。

·另一個pcie通道的未來擴展

·1.5 v和3.3 v電源

3、mini-sata(msata)變體

儘管共享mini pci express外形,但是msata插槽不一定與mini pci express兼容。因此,僅某些筆記本與msata驅動器兼容。大多數兼容系統都是基於英特爾的sandy bridge處理器架構,使用了huron river平台。 2011年3月至4月發布的聯想thinkpad t,w和x系列筆記本電腦在wwan卡槽中支持msata ssd卡。 thinkpad edge e220s / e420s以及lenovo ideapad y460 / y560也支持msata。

一些筆記本電腦(特別是華碩eee pc,蘋果macbook air以及戴爾mini9和mini10)使用pci express迷你卡作為固態硬碟。該變體使用預留和幾個非保留引腳來實現sata和ide接口直通,只保留usb,地面線,有時候還有核心pcie×1匯流排保持不變。這使得“minipcie”快閃記憶體和固態驅動器出售上網本大部分與真正的pci express mini實現不兼容。

此外,典型的華碩minipcie ssd長71毫米,導致戴爾51毫米的型號經常被錯誤地稱為半長。 2009年宣布推出一款真正的51 mm mini pcie ssd,具有兩個堆疊的pcb層,可以提供更高的存儲容量。被宣布的設計中保留了pcie接口,使其與標準的mini pcie插槽兼容。目前還沒有工業產品開發。

英特爾擁有眾多台式機主機板,其pcie×1迷你卡插槽通常不支持msata ssd。在英特爾支持網站上提供了pcie x1 mini-card插槽(通常與sata連線埠復用)本機支持msata的台式機主機板列表。

4、迷你pcie v2

新版本的mini pci express,m.2替代了msata標準。 通過m.2連線器提供的計算機匯流排接口是pci express 3.0(最多四個通道),serial ata 3.0和usb 3.0(後兩者的單個邏輯連線埠)。 這取決於主機支持和設備類型的所需級別,由m.2主機或設備的製造商決定要支持哪些接口。

5、pci express外部布線

pci express外部電纜pci express外部布線(也稱為外部pci express,電纜pci express或epcie)規格由pci-sig於2007年2月發布。

標準電纜和連線器已定義為×1,×4,×8和×16鏈路寬度,每個通道的傳輸速率為250 mb / s。 pci-sig也期望規範將演進到500 mb / s,如pci express 2.0。 最大電纜長度保持不變。 使用電纜pci express的一個例子是一個金屬外殼,其中包含許多pci插槽和pci-to-epcie適配器電路。 如果沒有epcie規範,此設備將無法實現。

衍生形式

其他幾種類型的擴展卡來自pcie,這些包括:

·高低卡

·expresscard:pc卡的後續版本(帶×1個pcie和usb 2.0;可熱插拔)

·pci express expressmodule:為伺服器和工作站定義的熱插拔模組化形式

·xqd卡:compactflash協會的基於pci express的快閃記憶體卡標準

·xmc:類似於cmc / pmc外形(vita 42.3)

·advancedtca:對更大套用的compactpci的補充;支持基於串列的背板拓撲

·amc:對advancedtca規範的補充;支持atca板上的處理器和i / o模組(×1,×2,×4或×8 pcie)。

·featurepak:適用於嵌入式和小型套用的小型擴展卡格式(43×65 mm),可在高密度連線器以及usb,i2c和多達100個i / o點上實現兩個1 pcie連線

·通用io:super micro computer inc的一款變體,專門用於低調機架式機箱。它的連線器支架相反,因此它不能裝在普通的pci express插座中,但它是引腳兼容的,如果拆下支架,可以插入。

·thunderbolt:intel的一個變體,它結合了displayport和pcie協定,與mini displayport兼容。 thunderbolt 3.0還結合了usb 3.1,並使用usb type-c外形尺寸,而不是mini displayport。

·串列數字視頻輸出:一些9xx系列英特爾晶片組允許將集成視頻的另一個輸出添加到pcie插槽(主要是專用和16通道)。

·m.2(以前稱為ngff)

·m-pcie通過m-phy物理層將pcie 3.0帶到移動設備(如平板電腦和智慧型手機)

·u.2(以前稱為sff-8639)

歷史版本

在早期開發中,pcie最初被稱為hsi(用於高速互連),並在最終確定其pci-sig名稱pci express之前,將其名稱更改為3gio(第三代i / o)。 名為阿拉帕霍工作組(awg)的技術工作組制定了該標準。 對於初稿,特設工作組只包括英特爾工程師; 隨後特設工作組擴大到包括行業夥伴。

pci express是一項不斷發展和完善的技術。

截至2013年,pci express版本4已經起草,預計在2017年將達到最終規格。在2016年pci sig的年度開發者大會上和英特爾開發者論壇上,synopsys展示了一款在pcie 4.0上運行的系統,而mellanox提供了一個合適的網卡。

pci express 版本 | 行代碼 | 傳輸速率 | 吞吐量 | |||

×1 | ×4 | ×8 | ×16 | |||

1.0 | 8b/10b | 2.5/s | 250/s | 1/s | 2gb/s | 4gb/s |

2.0 | 8b/10b | 5gt/s | 500mb/s | 2gb/s | 4gb/s | 8gb/s |

3.0 | 128b/130b | 8gt/s | 984.6mb/s | 3.938gb/s | 7.877gb/s | 15.754gb/s |

4.0 | 128b/130b | 16gt/s | 1.969gb/s | 7.877gb/s | 15.754gb/s | 31.508gb/s |

5.0 | 128b/130b | 32 or 25gt/s | 3.9 or 3.08gb/s | 15.8 or 12.3gb/s | 31.5 or 24.6gb/s | 63.0 or 49.2gb/s |

pcie 1.0a

2003年,pci-sig推出了pcie 1.0a,每通道數據速率為250 mb / s,傳輸速率為每秒2.5 gigatransfer(gt / s)。 傳輸速率表示為每秒傳輸量,而不是每秒位數,因為傳輸量包括不提供額外吞吐量的開銷位; pcie 1.x使用8b / 10b編碼方案,導致占用了20% (= 2/10)的原始信道頻寬。

pcie 1.1

2005年,pci-sig推出了pcie 1.1。 此更新的規範包括澄清和幾項改進,但與pci express 1.0a完全兼容。 數據速率沒有變化。

pcie 2.0

pci-sig於2007年1月15日宣布推出pci express base 2.0規範。pcie 2.0標準將pcie 1.0至5 gt / s的傳輸速率提高了一倍,每通道吞吐量從250 mb / s上升到500 mb / s。因此,32通道pcie連線器(×32)可支持高達16 gb / s的總吞吐量。

pcie 2.0主機板插槽與pcie v1.x卡完全向後兼容。 pcie 2.0卡也通常使用pci express 1.1的可用頻寬向下兼容pcie 1.x主機板。總體來說,為v2.0設計的顯示卡或主機板將與另一個v1.1或v1.0a配合使用。

pci-sig還表示,pcie 2.0具有對點對點數據傳輸協定及其軟體架構的改進。

英特爾首款支持pcie 2.0的晶片組是x38,截至2007年10月21日,各種廠商(abit,asus,gigabyte)開始出貨。amd開始使用其amd 700晶片組系列支持pcie 2.0,nvidia從mcp72開始。intel的所有晶片組,包括intel p35晶片組,都支持pcie 1.1或1.0a。

像1.x一樣,pcie 2.0使用8b / 10b編碼方案,因此每通道提供5 gt / s原始數據速率的有效4 gbit / s最大傳輸速率。

pcie 2.1

pci express 2.1(其規範日期為2009年3月4日)支持計畫在pci express 3.0中全面實施的大部分管理,支持和故障排除系統。 但是,速度與pci express 2.0相同。 不幸的是,插槽功率的增加打破了pci express 2.1卡和1.0 / 1.0a的一些較舊的主機板之間的向後兼容性,但是大多數具有pci express 1.1連線器的主機板都由廠商通過實用程式提供bios更新,以支持向後兼容性 的pcie 2.1。

pcie 3.0

pci express 3.0基本規範版本3.0在多個延遲之後於2010年11月提供。 2007年8月,pci-sig宣布pci express 3.0將以每秒8吉比特的速度(gt / s)進行比特率,並且將與現有的pci express實現向後兼容。當時還宣布,pci express 3.0的最終規範將延遲到2010年第二季度。pci express 3.0規範的新功能包括增強信令和數據完整性的一些最佳化,包括發射機和接收機均衡,pll改進,時鐘數據恢復和當前支持的拓撲的通道增強。

pci-sig的分析發現,在pci-sig互連頻寬擴展的可行性方面進行了為期6個月的技術分析,發現每秒8個千兆傳輸速率可以在主流矽工藝技術中製造,並且可以部署在現有的低成本材料和基礎設施上,同時保持對pci express協定棧的完全兼容性(可忽略不計的影響)。

pci express 3.0將編碼方案從之前的8b / 10b編碼升級到128b / 130b,將頻寬開銷從pci express 2.0的20%降低到大約1.54%(= 2/130)。這通過稱為“加擾”的技術來實現,該技術將已知的二進制多項式套用於反饋拓撲中的數據流。因為加擾多項式是已知的,所以可以通過使用反多項式的反饋拓撲運行數據來恢複數據。 pci express 3.0的8 gt / s比特率有效地提供每通道985 mb / s,實際上相對於pci express 2.0的通道頻寬翻倍

2010年11月18日,pci特別興趣小組正式向其成員發布了完成的pci express 3.0規範,以便根據新版本的pci express構建設備。

pcie 3.1

2013年9月,pci express 3.1規格已經宣布在2013年底或2014年初發布,在三個方面整合了pci express 3.0規範的各種改進:電源管理,性能和功能它於2014年11月發布。

pcie 4.0

2011年11月29日,pci-sig宣布pci express 4.0提供16gb / s比特率,使pci express 3.0提供的頻寬增加一倍,同時保持軟體支持和二手機械接口的向後兼容性。 pci express 4.0規格也將帶來oculink-2,這是thunderbolt連線器的替代品。 oculink版本2將具有高達16 gt / s(總共8gb / s×4通道),而thunderbolt 3連線器的最大頻寬為5gb / s。 另外,還要研究主動和空閒功率最佳化。 最終規格預計將於2017年發布。

在2016年8月,synopsys在英特爾開發者論壇上展示了運行pcie 4.0的測試機。 他們的智慧財產權已經授權給幾家計畫在2016年底提供其晶片和產品的公司。

pci-e sd 7.0

2018年6月,sd協會已經基本完成了全新一代sd 7.0標準規範的制定工作,計畫在2018年6月26-28日上海舉辦的mwc大會上正式公布。

擴展和未來方向

一些供應商提供pcie光纖產品,但這些通常僅在特定情況下才能使用,其中透明pcie橋接優於使用更主流的標準(如infiniband或乙太網),可能需要額外的軟體支持它當前的實現集中於距離而不是原始頻寬,並且通常不實現全×16鏈路。

thunderbolt由英特爾和蘋果公司共同開發,作為將displayport連線埠組合在一起的通用高速接口,最初旨在成為全光纖接口,但由於創建消費者友好的光纖互連大多數早期實現是混合銅纖維系統。一個顯著的例外,sony vaio z vpc-z2使用帶有光學組件的非標準usb連線埠連線到外置pcie顯示適配器。蘋果一直是2011年thunderbolt採用的主要動力,儘管其他幾家供應商已經宣布推出具有thunderbolt的新產品和系統。

移動pcie規範(縮寫為m-pcie)允許pci express架構在mipi alliance的m-phy物理層技術上運行。基於已經廣泛採用的m-phy及其低功耗設計,移動pcie允許pci express在平板電腦和智慧型手機中使用。

oculink(代表“光銅鏈路”)是“電纜版pci express”的擴展,作為thunderbolt接口版本3的競爭對手。將於2015年秋季發布的oculink版本1.0支持通過銅纜布線的pcie 3.0 x4通道(8 gt / s,3.9 gb / s)光纖版可能會在將來出現。

硬體協定摘要

pcie鏈路是圍繞稱為通道的串列(1位)點對點連線的專用單向耦合的。 這與早期的pci連線形成鮮明對比,pci連線是基於匯流排的系統,其中所有設備共享相同的雙向32位或64位並行匯流排。

pci express是一種分層協定,由事務層,數據鏈路層和物理層組成。 數據鏈路層被細分為包括媒體訪問控制(mac)子層。 物理層被細分為邏輯和電子子層。 物理邏輯子層包含物理編碼子層(pcs)。 這些術語借鑑了ieee 802網路協定模型。

物理層

pcie物理層(phy,pciephy,pci express phy或pcie phy)規範分為兩個子層,對應於電氣和邏輯規範。邏輯子層有時被進一步劃分為mac子層和pcs,儘管該劃分不是pcie規範的正式部分。英特爾公布的pci express(pipe)phy接口(58)定義了mac / pcs功能分區以及這兩個子層之間的接口。 pipe規範還標識了物理介質連線(pma)層,其中包括串列器/解串器(serdes)和其他模擬電路;然而,由於serdes實現在asic供應商之間差異很大,pipe沒有指定pcs和pma之間的接口。

在電平上,每個通道由兩個以2.5,5,8或16 gbit / s為單位的單向lvds對組成,具體取決於協商的能力。傳送和接收是單獨的差分對,每個通道總共有四條數據線。

任何兩個pcie設備之間的連線稱為鏈路,並且由一個或多個通道的集合構建。所有設備必須最低限度地支持單通道(×1)鏈路。設備可以可選地支持由2,4,8,12,16或32個通道組成的更寬的鏈路。這樣可以通過兩種方式實現非常好的兼容性:

pcie卡在任何至少與其一樣大的插槽中物理適配(並且正常工作)(例如,x尺寸的卡將在任何大小的插槽中工作);

只要提供較大物理槽所需的地面連線,則物理尺寸較大(例如×16)的槽可以更少的通道連線(例如,×1,×4,×8或×12)尺寸。

在這兩種情況下,pcie協商最高相互支持的通道數。驗證了許多顯示卡,主機板和bios版本,以支持同一連線上的×1,×4,×8和×16連線。

儘管這兩者將是信號兼容的,但通常不可能將一個物理上更大的pcie卡(例如,×16尺寸的卡)放置在較小的插槽中 - 儘管如果pcie插槽被更改或者使用了提升板,大多數主機板會允許這個。 pcie連線器的寬度為8.8 mm,高度為11.25 mm,長度可變。連線器的固定部分長度為11.65mm,包含兩行11(總共22個),另一部分的長度根據通道數量而變化。引腳以1mm間隔隔開,進入連線器的卡的厚度為1.8mm。

數據傳輸

pcie通過與數據相同的連結傳送所有控制訊息,包括中斷。串列協定永遠不會被阻止,所以延遲仍然與具有專用中斷線的常規pci相當。

在多通道鏈路上傳送的數據被交織,這意味著每個連續的位元組被連續通過。 pcie規範將這種交織作為數據條帶化。在需要大量硬體複雜性來同步(或去偏移)輸入條帶數據的同時,條帶化可以顯著減少鏈路上第n個位元組的延遲。雖然通道沒有緊密同步,但對於2.5 / 5/8 gt / s,通道偏差為20/8/6 ns,因此硬體緩衝區可以重新對齊條帶數據。由於填充要求,條帶化可能不一定會降低鏈路上的小數據包的等待時間。

與其他高數據速率串列傳輸協定一樣,時鐘嵌入在信號中。在物理層面上,pci express 2.0使用8b / 10b編碼方案來確保連續相同數字(零或1)的字元串的長度有限。該編碼用於防止接收機丟失位邊緣的位置。在這種編碼方案中,每個八(未編碼)有效載荷數據位被替換為傳送數據的10(編碼)比特,導致電頻寬中的20%開銷。為了提高可用頻寬,pci express 3.0版代替使用128b / 130b編碼加擾。 128b / 130b編碼依賴於加擾來限制數據流中相同數字串的運行長度,並確保接收機保持同步到發射機。它還通過防止傳送的數據流中的重複數據模式來降低電磁干擾(emi)。

數據鏈路層

數據鏈路層為pcie express鏈路執行三個重要服務:

對由事務層生成的事務層數據包(tlp)進行排序,

通過確認協定(ack和nak信令)確保在兩個端點之間可靠地傳遞tlp,這些確認協定明確要求重播未確認/不良tlp,

初始化和管理流量控制信用

在傳送側,數據鏈路層為每個輸出tlp生成遞增序列號。它作為每個傳輸的tlp的唯一標識標籤,並被插入到出站tlp的頭部。 32位循環冗餘校驗碼(在本上下文中稱為鏈路crc或lcrc)也附加到每個輸出tlp的末尾。

在接收端,接收的tlp的lcrc和序列號都在鏈路層中被驗證。如果lcrc檢查失敗(指示數據錯誤)或序列號超出範圍(從上一次有效接收到的tlp不連續),則壞tlp以及在壞tlp之後接收的任何tlp,被認為是無效和被丟棄。接收方向無效tlp的序列號傳送一個否定的確認訊息(nak),請求重新傳送該序列號的所有tlp。如果接收的tlp通過lcrc檢查並具有正確的序列號,則被視為有效。鏈路接收器增加序列號(跟蹤最後接收的良好tlp),並將有效的tlp轉發到接收者的事務層。 ack訊息被傳送到遠程發射機,指示tlp被成功地接收(並且擴展了所有具有過去序列號的tlp)。

如果發射機接收到nak訊息,或者在逾時時間段到期之前沒有接收到確認(nak或ack),則發射機必須重發所有缺少肯定確認(ack)的tlp。除了設備或傳輸介質的持續故障之外,鏈路層提供與事務層的可靠連線,因為傳輸協定確保在不可靠介質上傳送tlp。

除了傳送和接收由事務層生成的tlp之外,數據鏈路層還生成並消耗dllp,數據鏈路層數據包。 ack和nak信號通過dllp進行通信,流控信用信息,一些電源管理訊息和流控信用信息(代表事務層)也是如此。

實際上,鏈路上的未確認tlp的數量受到兩個因素的限制:發射機的重播緩衝區的大小(必須存儲所有傳送的tlp的副本,直到遠程接收機確認它們),以及流量控制接收機發給發射機的信用。 pci express要求所有接收者發出最少數量的信用,以保證一個鏈路允許傳送pciconfig tlp和訊息tlp。

事務層

pci express實現拆分事務(具有請求和回響時間間隔的事務),允許連結攜帶其他流量,而目標設備收集回響的數據。

pci express使用基於信用的流量控制。在該方案中,設備在其事務層中為每個接收到的緩衝器通告初始信用量。連結相對端的設備在向該設備傳送交易時,會計算每個tlp從其帳戶中消耗的信用數量。傳送設備只能在這樣做時才傳輸tlp,使其消費的信用計數不超過其信用限額。當接收設備從其緩衝區完成tlp的處理時,它向傳送設備發出信用回報信號,從而將信用額度增加了恢復的數量。信用計數器是模組化計數器,消費信用與信用限額的比較需要模數運算。這種方案的優點(與其他方法,如等待狀態或基於握手的傳輸協定相比)是信用回報的延遲不會影響性能,前提是不會遇到信用額度。如果每個設備設計有足夠的緩衝區大小,則通常滿足這一假設。

經常引用pcie 1.x,以支持每個方向每個通道250 mb / s的數據速率。這個數字是從物理信令速率(2.5千兆位)除以編碼開銷(每個位元組10位)的計算。這意味著十六行(×16)pcie卡理論上能夠達到16×250 mb / s =每個方向4 gb / s。雖然這在數據位元組方面是正確的,但更有意義的計算是基於可用的數據有效載荷速率,這取決於流量的簡檔,這是高級(軟體)應用程式和中間協定級別的函式。

像其他高數據速率串列互連繫統一樣,由於附加的傳輸魯棒性(crc和確認),pcie具有協定和處理開銷。長時間連續的單向傳輸(例如高性能存儲控制器中的那些)可以接近pcie的原始(通道)數據速率的95%。這些轉移也可以從增加通道數量(×2,×4等)中獲得最大收益。但是在更典型的套用(如usb或乙太網控制器)中,流量簡檔的特徵是具有頻繁強制確認的短數據包。由於分組解析和強制中斷(在設備的主機接口或pc的cpu)中的開銷,這種流量會降低鏈路的效率。作為連線到相同印刷電路板的設備的協定,它不需要與用於長距離通信的協定的傳輸錯誤相同的容限,因此這種效率的損失對於pcie不是特別的。

套用

pci express在消費者,伺服器和工業套用中運行,作為主機板級互連(連線主機板外圍設備),無源背板互連以及作為附加板的擴展卡接口。

在幾乎所有現代(截至2012年)pc(從消費者筆記本電腦和台式機到企業數據伺服器)中,pcie匯流排作為主要的主機板級互連,將主機系統處理器與集成外設(表面貼裝ic)連線起來,和附加外設(擴展卡)。在大多數這些系統中,pcie匯流排與一個或多個傳統pci匯流排共存,以便與大量傳統pci外設的向後兼容。

截至2013年,pci express已將agp替換為新系統上顯示卡的默認界面。 amd(ati)和nvidia自2010年以來發布的幾乎所有型號的顯示卡都使用pci express。 nvidia使用pcie的高頻寬數據傳輸作為其可擴展鏈路接口(sli)技術,它允許同一晶片組和型號的多個顯示卡串聯運行,從而提高性能。 amd還開發了基於pcie的多gpu系統,稱為crossfire。 amd和nvidia發布了支持多達四個pcie×16插槽的主機板晶片組,允許三gpu和四gpu卡配置。

外部gpu

理論上,通過將筆記本電腦與任何pcie桌面顯示卡(封裝在自己的外部外殼中,具有強大的電源和散熱)連線,外部pcie可以為筆記本電腦提供桌面的圖形功能;可能使用expresscard接口或thunderbolt接口。 expresscard接口提供5 gbit / s(0.5 gb / s吞吐量)的比特率,而thunderbolt接口提供高達40 gbit / s(5 gb / s吞吐量)的比特率。

2010年推出的外部卡集線器可以通過pci expresscard插槽連線到筆記本電腦或台式機。這些集線器可以接受全尺寸顯示卡。示例包括msi gus, village instrument的vidock,華碩xg站,bplus pe4

asus nvidia geforce gtx 650 ti

asus nvidia geforce gtx 650 tih v3.2適配器以及更多即興diy設備。然而,這樣的解決方案受到筆記本電腦上可用的pcie插槽的大小(通常只有x1)和版本的限制。

2008年,amd宣布推出ati xgp技術,該技術基於與pcie×8信號傳輸兼容的專有布線系統。富士通amilo和acer ferrari one筆記本電腦提供此連線器。富士通此後推出了針對xgp的amilo graphicbooster外殼。2010年左右,宏碁推出了xgp的dynavivid圖形碼頭英特爾霹靂接口給了新的和更快速的產品與外部與pcie卡連線的機會。 magma發布了expressbox 3t,可容納三個pcie卡(兩個在×8,一個在×4)。msi還發布了專門用於顯示卡的pcie底盤thunderbolt gus ii。其他產品,如sonnet的echo express和mlogi的mlink是thunderbolt pcie機箱,尺寸較小然而,所有這些產品都需要具有thunderbolt連線埠(即thunderbolt設備)的計算機,例如,蘋果macbook pro在2013年秋季發布。

對於專業市場,nvidia開發了可用於高級圖形套用的quadro plex外部pcie系列gpu。這些視頻卡需要一個pci express×8或×16插槽,用於通過支持8個pcie通道的vhdci連線到plex的主機側卡。

存儲設備

pci express協定可用作快閃記憶體設備的數據接口,如存儲卡和固態硬碟(ssd)。 an_intel_82574l_gigabit_ethernet_nic

an_intel_82574l_gigabit_ethernet_nic

an_intel_82574l_gigabit_ethernet_nic

an_intel_82574l_gigabit_ethernet_nicxqd卡是使用由compactflash協會開發的pci express的存儲卡格式,傳輸速率高達500 mb / s

許多高性能企業級ssd被設計為具有直接放置在電路板上的快閃記憶體晶片的pci express raid控制器卡,利用專有接口和定製驅動程式與作業系統進行通信;與串列ata或sas驅動器相比,這允許高得多的傳輸速率(超過1 gb / s)和iops(每秒超過一百萬個i / o操作)例如,2011年,ocz和marvell共同開發了一款用於pci express 3.0×16插槽的本地pci express固態驅動器控制器,最大容量為12 tb,性能達到7.2 gb / s,連續傳輸和高達252萬隨機轉移中的iops。

sata express是連線ssd的接口,通過為連線的存儲設備提供多個pci express通道作為純pci express連線。m.2是內部安裝的計算機擴展卡和相關連線器的規範,也使用多個pci express通道。

pci express存儲設備可實現ahci邏輯接口以實現向後兼容,還可實現nvm express邏輯接口,通過利用此類設備提供的內部並行性提供更快的i / o操作。企業級ssd也可以通過pci express實現scsi。

群集互連

某些數據中心套用(如大型計算機集群)由於銅線纜固有的距離限制,需要使用光纖互連。 通常,諸如乙太網或光纖通道的面向網路的標準對於這些套用來說足夠,但是在某些情況下,由可路由協定引入的開銷是不期望的,並且需要諸如infiniband,rapidio或numalink之類的較低級別的互連。 本地匯流排標準(如pcie和hypertransport)原則上可以用於此目的,但截至2015年,解決方案只能從海豚供應商(如海豚ics)獲得。 sata_6_gbit-s_controller,_in_form_of_a_pci_express_card

sata_6_gbit-s_controller,_in_form_of_a_pci_express_card

sata_6_gbit-s_controller,_in_form_of_a_pci_express_card

sata_6_gbit-s_controller,_in_form_of_a_pci_express_cardpci-e 3.0

常見的顯示卡都是pci-e 2.0標準的,制定於2007年,速率5gt/s,x16通道頻寬可達8gb/s。按照原先的路線圖,pci-e 3.0標準將在2010年進入市場,不過實際上卻是2010年才完成pci-e 3.0標準的最終方案,而直到一年後hd 7970發布才真正有顯示卡支持pci-e 3.0。

pci-e 3.0:頻寬更高、延遲更低

與pci-e 2.0相比,pci-e 3.0的目標是頻寬繼續翻倍達到10gb/s,要實現這個目標就要提高速度,pci-e 3.0的信號頻率從2.0的5gt/s提高到8gt/s,編碼方案也從原來的8b/10b變為更高效的128b/130b,其他規格基本不變,每周期依然傳輸2位數據,支持多通道並行傳輸。

除了頻寬翻倍帶來的數據吞吐量大幅提高之外,pci-e 3.0的信號速度更快,相應地數據傳輸的延遲也會更低。此外,針對軟體模型、功耗管理等方面也有具體最佳化。簡而言之,pci-e 3.0就跟高速路一樣,車輛跑得更快,發車間隔更低,座位更舒適。

pci-e 3.0 要求

·支持多個細分市場和新興套用:

統一桌面,移動,工作站,伺服器,通信平台和嵌入式設備的i / o架構;

·提供低成本,大批量解決方案的能力:

成本在系統級以下pci成本結構或以下

·支持多平台互聯使用:

晶片到晶片,板對板連線器或電纜

·新的機械外形:

移動式,類似pci的外形尺寸和模組化,車架尺寸

·pci兼容軟體模型:

能夠枚舉和配置pci express硬體,無需修改即可使用pci系統配置軟體實現,;

無需修改即可啟動現有作業系統

無需修改即可支持現有i / o設備驅動程式,

能夠配置/ 通過pci實現新的pci express功能

·性能:

·低開銷,低延遲通信,最大限度地提高套用有效載荷頻寬和鏈路效率;

·每個引腳的高頻寬,最大限度地減少每個設備的引腳數和連線器接口;

·通過聚合通道和信號頻率可擴展的性能

高級功能:

了解不同的數據類型和排序規則,電源管理和預算,

識別給定功能的電源管理功能

·將功能轉換為特定電源狀態

·接收功能當前電源狀態通知

·產生從主電源關閉狀態喚醒的請求,

·將設備上電順序的能力設定為允許在功率預算中實現平穩的平台策略

支持差異化服務的能力,即不同的服務質量

能夠為服務質量的數據流量提供專用的鏈路資源,以提高面向線路阻塞的結構效率和有效的套用級性能

在每個組件中配置服務質量仲裁策略

能夠標記每個數據包的端到端服務質量

創建端到端等時(基於時間,注入速率控制)解決方案

·熱插拔和熱插拔支持

支持現有pci熱插拔和熱插拔解決方案

支持本地熱插拔和熱插拔解決方案(無需框線信號)

支持所有形式因素的統一軟體模型

·數據完整性:

·支持所有類型的事務和數據鏈路數據包的鏈路級數據完整性

·支持高可用性解決方案的端到端數據完整性

·故障處理:

·能夠支持高級錯誤報告和處理,以改進故障隔離和恢復解決方案

·工藝技術獨立性:

·在發射機和接收機上支持不同直流共模電壓

·易於測試:

·通過簡單連線測試設備測試符合性

pci express 鏈路

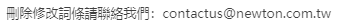

一個鏈路表示兩個組

件之間的雙單工通信通道。基本的pci express鏈路由兩個低電壓,差分驅動信號對組成:傳送對和接收對,如圖所示

基本連結:pci express鏈路由雙向單向差分鏈路組成,實現為傳送對和接收對。使用編碼方案嵌入數據時鐘以實現非常高的數據速率

信令速率:一旦初始化,每個鏈路只能在支持的信令級別之一運行。對於第一代pci express技術,只有一個信令速率被定義,提供有效的每秒每通道每個方向2.5吉比特的原始頻寬。第二代提供有效的每秒每通道每個方向8.0吉比特的原始頻寬。隨著未來的技術進步,數據速率預計將增加。

通道:鏈路必須支持至少一個通道,每個通道表示一組差分信號對(一對用於傳輸,一對用於接收)。為了縮放頻寬,鏈路可以聚合由xn表示的多個通道,其中n可以是任何 的支持鏈路寬度。以2.5gt / s數據速率運行的x8鏈路表示每個方向的原始頻寬為20千兆位的聚合頻寬

初始化:在硬體啟動期間,每個pci express鏈路都是在鏈路兩端的兩個代理商的通道寬度和操作頻率協商後設定的。沒有固件或作業系統軟體

對稱性:每個鏈路必須支持對稱數,如果在每個方向上的通道,即x16鏈路指示在每個方向上存在16個差異信號對

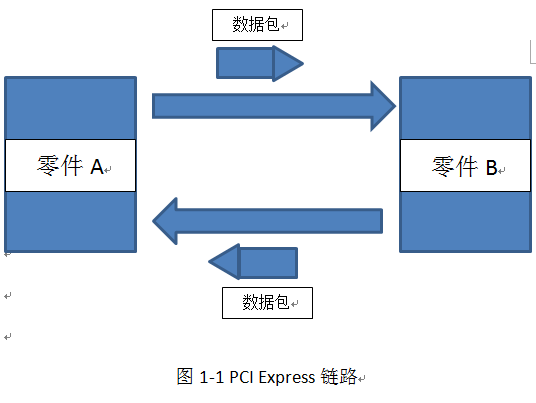

pci express fabric拓撲

結構是由連線一組組件的點對點鏈路組成,一個示例性結構拓撲如圖1-2所示。這個圖說明了一個層次結構的單個結構實例,由一個根複合體組成,多個端點(i / o設備),交換機和pci express標準的 pci / pci-x橋接器,均通過pci express鏈路互連。

pci-e 4.0

pci express 3.0是企業計算的記憶,微處理器,網路和存儲之間的通信的主要標準,但它正面臨新的競爭,因為其即將到來的重大更新是一些最重要的觀察者所壓倒的。

控制規範的pci-sig官員在五年前就談到了他們的第四代計畫,並表示版本4.0將於2015年到期。現在,新的延遲,加上大數據,網際網路的最新趨勢物聯網和移動計算領域正在推動數個頂尖it廠商採用新的數據瓶頸方法。

據了解,pcie 4.0將以每秒16千兆位傳輸的速度移動數據,這是當前版本的兩倍。 pci-sig主管的工程師,ibm的al yanes解釋說,這可以通過使用更短時間傳送大量數據的突發方法來實現當前電壓水平的一半或四分之一。

yanes去年宣布,pcie 4.0將在今年年初推出。現在,由於測試問題,“我認為在循環推出之前的第三季度會更多,”他說。他補充說,直到最近還沒有太多的需求。

pcie 4.0,具有16gt / s的數據速率和新的連線器將在2017年完成。

pci express匯流排已經發展十多年了。到目前為止,技術的初始數據速率已翻了三倍,但下一步是花費更長的時間。 pci sig聲稱,第四代pci express規範將於2017年完成,並將在這十年中實現。新技術將使用新的連線器,並將是pci express的最後一個銅版本。

pci sig [特殊興趣小組]自2011年年底以來一直在開發pci express 4.0。新車的目標數據速率為每通道16gt / s [每秒千兆轉發],組織一直設定這個目標,即使許多沒有相信使用寬泛的銅線互連匯流排是可行的。該標準尚未定稿,因為參與者必須同意許多參數,包括互連屬性,結構管理以及設計和構建符合pci express 4.0規範的系統和外設所需的編程接口。

例如,到目前為止,pci sig尚未就沒有重新定時器的pcie 4.0軌跡的最大長度達成一致。許多套用,如伺服器和通信設備,需要更長的互連。

pci sig總裁al yanes在接受ee times採訪時表示:“我們正在獲得16gt / s,幾年前沒有人想到可能。” “基地距離仍在驗證中,但通常為7英寸左右。 15英寸左右的兩個連線器的更長的通道將具有重新定時器,但第3代已經使用了重新定時器 - 現在我們需要將它們用於較短的通道。

競爭協定

基於高頻寬串列架構的其他通信標準包括infiniband,rapidio,hypertransport,intel quickpath interconnect和移動行業處理器接口(mipi)。差異基於靈活性和可擴展性與延遲和開銷之間的權衡。例如,將複雜的報頭信息添加到傳輸的分組允許複雜路由(pci express能夠通過可選的端到端tlp前綴功能)。額外的開銷降低了接口的有效頻寬,並使匯流排發現和初始化軟體複雜化。此外,使系統可熱插拔要求軟體跟蹤網路拓撲變化。 infiniband是一種這樣的技術。

另一個例子是使數據包更短以減少延遲(如果匯流排必須作為存儲器接口運行,則需要這樣做)。較小的數據包意味著數據包頭消耗的數據包的百分比較高,從而降低了有效頻寬。為此目的設計的匯流排協定的例子是rapidio和hypertransport。

pci express位於中間的某個地方,以設計為目標,作為系統互連(本地匯流排),而不是設備互連或路由網路協定。此外,其軟體透明度的設計目標限制了協定並稍微提高了其延遲。

pcie 4.0實現的延遲導致了gen-z聯盟,ccix的努力和一個開放的coherent accelerator處理器接口(capi),全部在2016年底之前被公布。