鏗騰電子科技有限公司(cadence design systems, inc; :cdns)是一個專門從事()的軟體公司,由sda systems和ecad兩家公司於1988年兼併而成。是全球最大的電子設計技術(electronic design technologies)、程式方案服務和設計服務供應商。其解決方案旨在提升和監控半導體、計算機系統、網路工程和電信設備、以及其它各類型電子產品的設計。產品涵蓋了電子設計的整個流程,包括系統級設計,功能驗證,ic綜合及布局布線,模擬、混合信號及射頻ic設計,全定製,ic物理驗證,pcb設計和硬體仿真建模等。 其總部位於美國聖何塞(san jose),在全球各地設有銷售辦事處、設計及研發中心。2016年,cadence被《財富》雜誌評為“全球年度最適宜工作的100家公司”。

基本介紹

- 公司名稱:鏗騰電子科技有限公司

- 外文名稱:cadence design systems

- 成立時間:1988年

- 簡稱:cadence

公司簡介,國內概況,設計平台,中國區分銷商,培訓內容,產品介紹,底層軟體,軟體管理最佳化,揭開面紗,大學計畫,

公司簡介

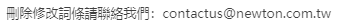

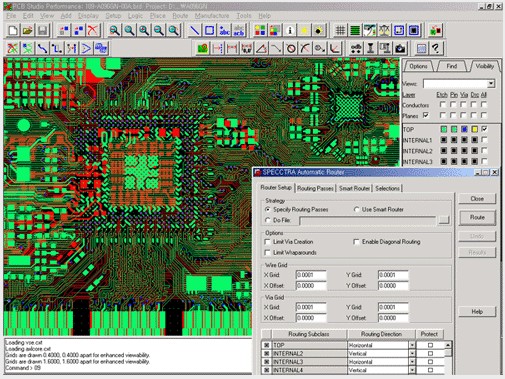

cadence公司的(electronic design automation)以提供設計方法學服務,幫助客戶最佳化其設計流程;提供設計外包服務,協助客戶進入新的市場領域。自1991年以來,該公司已連續在國際eda市場中銷售業績穩居第一。全球知名半導體與公司均將cadence軟體作為其全球設計的標準。cadence公司其總部位於美國聖何塞(san jose),在全球各地設有銷售辦事處、設計及研發中心,現擁有員工約4800名,2003年收入約11億美元。 cadence設計軟體

cadence設計軟體

cadence設計軟體

cadence設計軟體國內概況

cadence中國現擁有員工400多人,擁有北京和上海兩個研究開發中心,銷售網路遍布全國。cadence在上海先後建立了高速系統技術中心和企業服務中心,為用戶提供高質量、有效的專業設計和外包服務。cadence北京研發中心主要承擔與美國總部eda軟體研發任務,力爭提供給用戶更加完整的設計工具和全流程服務。 cadence 公司2003年斥5000萬美元巨資在北京投資建立的中關村-cadence軟體學院,立志為中國電子行業培養更多面向和的高級設計人才。

設計平台

cadence allegro系統互連平台能夠跨積體電路、封裝和pcb高性能互連。套用平台的協同設計方法,工程師可以迅速最佳化i/o緩衝器之間和跨積體電路、封裝和pcb的系統互聯。該方法能避免硬體返工並降低硬體成本和縮短設計周期。約束驅動的allegro流程包括高級功能用於設計捕捉、信號完整性和物理實現。由於它還得到cadence encounter與virtuoso平台的支持,allegro協同設計方法使得高效的設計鏈協同成為現實。

2008年6月17日,cadence對外公開了他們提交給mentor graphics公司董事會的收購方案,即以每股16美元的價格現金收購mentor graphics,交易總額達16億美元。

cadence表示,其現金收購價格高出6月16日(也就是cadence公開提案的最後一個交易日)mentor graphics收盤時普通股的30%。同時也比5月2日(cadence公司將其提案交給mentor時)mentor graphics公司收盤價時普通股票高出59 %。這一價格也比mentor graphics公司過去30個交易日中平均收盤價格高出46%。

在6月17日給mentor graphics董事會的信件中, cadence總裁兼ceo michael j. fister回想起他和mentor graphics總裁兼ceo walden c. rhines最初談及合併cadence和 mentor graphics是在2008年4月16日。不過,他表示很失望,因為rhines也不願意進行更進一步的談判。

在6月18日進行的新聞和分析師會議上,fister表示:“mentor graphics公司告訴我們,截至5月底他們都想要保持獨立,不希望進一步討論我們的收購方案,由於他們拒絕和我們談判,所以我們決定公開我們的收購方案。

在給rhines的信中,fister解釋了這一併購的意義,他寫道:“我們相信cadence和mentor graphics的聯合,將為客戶提供更廣泛和更全面的集成產品和技術組合,能夠更好地解決客戶在開發下一代產品時遇到的各種挑戰。”

fister補充說:“cadence和mentor graphics的合併,能夠集中我們各自的創新人才,從而提供更全面的尖端解決方案,為客戶提供一個全新水平的客戶體驗。通過共同努力,我們將加快客戶的創新速度和效率,更好滿足客戶開發新產品的需要。”

cadence提議的實現取決於能否達成雙方可接受的合併協定。

mentor公司(總部設在俄勒岡州,維爾市)約有4200名職員,過去12個月的收入約為8.5億美元。 而cadence公司2007年的收入為16.1億美元。

近期,cadence參與了許多收購。例如,在2008年3月, cadence收購了chip estimate 公司,這是一家ic規劃和ip復用的開發商。2007年8月,cadence收購了clear shape technologies,這是一家可製造性設計( dfm的)技術的開發商。一個月前,它收購了專業光刻公司invarium。

fister在新聞與分析師大會上表示:“在過去十年里,我們已經完成了36個不同的收購,這些公司所面臨的挑戰是一樣的。我們充分考慮了客戶解決方案的需求,同時展示了如何實現生產的有效性。存在很多因素,這也是迫不得已,處在客戶環境非常困難的時期,他們面臨著成本挑戰,合併是最佳時機。”啟程教育

中國區分銷商

日前,cadence公司已與中國最大的ic元器件分銷商、納斯達克上市公司(代碼:cogo)科通集團簽署分銷合作協定,授權後者為其中國區分銷商。

按照該協定,科通集團將在中國區授權分銷cadence的及全線產品。

培訓內容

1、allegro教學導入;

2、allegro基本操作及設計流程

3、allegro教學環境的設定 ;

4、orcad cis 軟體使用介紹

5、設計資料的導入;

6、設計規則初步設定;

7 、placement (元件布局)

8、layout技巧分享及介紹;

9、fill shape鋪銅介紹及操作嵌入式系統的訓練

10、power fill;

11、silkscreen處理;

12、assembly處理;

13、test point添加(測試點)

14、gerber資料的準備;

15、gerber資料的輸出;

16、cam350的基本使用

17、check list(檢查列表);

18、生產檔案輸出;

19、panel drawing(拼版)

20、制板要求填寫;

21、高速電路介紹;

22、constraint manger使用介紹

23、polar軟體介紹及使用;

24、pcba介紹;

25、pcb板廠流程介紹

26、可製造設計介紹;

27、高頻電路的設計;

28、盲埋孔設計介紹;

29、emi問題泛舟及應對措施;

30、電子元器件介紹;

31、封裝設計1(dip);

32、封裝設計2(smt)

33、pcb設計管理和組織;

34、skill介紹;

35、課程總結就測試

2、allegro基本操作及設計流程

3、allegro教學環境的設定 ;

4、orcad cis 軟體使用介紹

5、設計資料的導入;

6、設計規則初步設定;

7 、placement (元件布局)

8、layout技巧分享及介紹;

9、fill shape鋪銅介紹及操作嵌入式系統的訓練

10、power fill;

11、silkscreen處理;

12、assembly處理;

13、test point添加(測試點)

14、gerber資料的準備;

15、gerber資料的輸出;

16、cam350的基本使用

17、check list(檢查列表);

18、生產檔案輸出;

19、panel drawing(拼版)

20、制板要求填寫;

21、高速電路介紹;

22、constraint manger使用介紹

23、polar軟體介紹及使用;

24、pcba介紹;

25、pcb板廠流程介紹

26、可製造設計介紹;

27、高頻電路的設計;

28、盲埋孔設計介紹;

29、emi問題泛舟及應對措施;

30、電子元器件介紹;

31、封裝設計1(dip);

32、封裝設計2(smt)

33、pcb設計管理和組織;

34、skill介紹;

35、課程總結就測試

產品介紹

1、板級電路設計系統

包括原理圖輸入、生成、模擬數字/混合,fpga設計,pcb編輯和自動布局布線mcm電路設計、高速pcb版圖的設計仿真等等。包括:

* concept hdl原理圖設計輸入工具,有for nt和for unix的產品。

* check plus hdl原理圖設計規則。(nt & unix)

* spectra quest engineer pcb版圖布局規劃工具(nt & unix)

* allegro expert專家級pcb版圖編輯工具 (nt & unix)

* spectra expert autorouter 專家級pcb自動布線工具

* signoise信噪分析工具

* emcontrol檢查工具

* synplify fpga / cpld綜合工具

* hdl analyst hdl分析器

* advanced package designer先進的mcm封裝設計工具

2、alta系統級無線設計

這一塊的產品主要是套用於網路方面的,我個人以為。尤其是它包括有一套的gsm模型,很容易搞cdma等等之類的東西的開發。但是我覺得做信號處理和圖象處理也可以用它,因為它裡面內的spw太牛了,至少是看起來是,spw最牛的地方就是和hds的接口,和matlab的接口。matlab裡面的很多模型可以直接調入spw,然後用hds生成仿真代碼或者是hdl語言仿真代碼。(這我沒有license,沒有試過,看openbook上說的)。也就是說,要是簡單行事的話,就可以直接用matlab做個模型,然後就做到版圖了,呵呵。

alta主要有下面的一些package:

*(cierto signal processing work system)系統。

可以說,spw包括了matlab的很多功能,連demo都有點象,呵呵。它是面向的、仿真和實現的環境。它的通常的套用領域包括無線和有線載波通信、多媒體和網路設備。在進行算法設計、濾波器設計、c code生成、軟/硬體結構聯合設計和硬體綜合的理想環境。它裡面非常有意思的就是信號計算器。

* hds (hardware design system)硬體系統設計系統

它是的集成組件之一。包括仿真、庫和分析擴展部分。可以進行spw的定點分析行為級和rtl級的。

* mutimedia多媒體 (multimedia design kit)

我沒有見識過這部分的東東。在產品發布會的演示上看起來倒是很有意思。據說可以很快的生成一個多媒體的套用環境。它可以進行多媒體套用的設計,包括、數位電視等等以及任何種類的圖象處理系統的設計。

* 無線技術wireless(is-136 verification environment)

無線電技術標準系統級驗證工具,可以在系統級的抽象層上生成、開發和改進遵守is-54/136 標準的算法。在完成硬體結構設計後,就可以使用hds直接生成可綜合的hdl描述和相應的標準檢測程式()。

* is-95無線標準系統級驗證

* bones網路衉議分析和驗證的設計工具。

這個東東看起來很有意思。它是一套軟體系統,專門用來做結構和衉議的設計這個東東看起來很有意思。它是一套軟體系統,專門用來做多媒體網路結構和衉議的設計的。可以用來快速的生成和分析之間的信息流的抽象模型,並建立一個完整的無線網路的運作模型。例如,用戶可以改進atm轉換器的算法,並建立其基於包括高速快取和記憶體和匯流排、通信處理方法的套用模型。

* g、vcc 虛擬衉同設計工具包

它是用來進行基於可重用的ip核的系統級設計環境。

在上面的這些東西中,我覺得很重要的還是需要有庫的支持,例如在spw裡面就要有對應的不同的算法的hdl庫的支持,才能夠得到最後rtl級的實現。在大學版中,這些部分的license和部分bin代碼也沒有提供。

3、邏輯設計與驗證(ldv)設計

這部分的軟體大家都應該是很熟悉的,因為pc版的d版好象已經很普及了。^-^這裡簡單介紹一下cadence的ldv流程,雖然感覺大家用synopsys還是居多。

首先是老闆產生一個創意,然後就是設計人員(學生)使用vhdl或者是verilog語言對設計來進 行描述,生成hdl代碼。然後,可以用 verilog-xl, nc-verilog, leapfrogvhdl nc-vhdl等工具來進行行為級仿真,判斷設計的可行性,驗證模組的功能和設計的debug。然後是調試和分析環境中使用代碼處理箱(verisure/for verilog) (vhdlcover/for vhdl)分析仿真結果,驗證測試級別。然後用ambit buildgates進行綜合,並使用綜合後的時延估計(sdf檔案)來進行門級仿真,然後再使用verifault進行故障仿真。

以上是很簡單的一個流程,實際上系統級設計後,就應該進行設計仿真的,要是設計是一個大的模組的話。而且在綜合的時候,寫綜合限制檔案也是很麻煩的,要求很多次的反覆。上面的流程還不包括測試的加入(如掃描啦什麼的)。上面的流程對於小設計是可以的。

ldv包括的模組有下面的這些東西:

* verilog-xl

* leapfrog vhdl仿真器

支持混合語言的仿真,其的仿真是通過編譯後仿真,加快了速度。

* affirma nc verilog仿真器

其主要的特點是適合於大系統的仿真。

* affirma nc vhdl仿真器

適用於的仿真。

* affirema 形式驗證工具--等價檢驗器

* verifault-xl 故障

感覺故障仿真是最費時間的仿真步驟。用來測試晶片的可測性設計的。

* verisure代碼覆蓋率

* envisia build gates 綜合工具

ambit 的buildgates的特性中,我覺得最好用的應該是它的pks的feature,當然,呵呵我沒有它的license。因為在pks feature中,ambit可以調用se的pdp等物理布局工具來進行時延估計。這樣的話,我覺得它的timing 會比synopsys要好。在我試過的synopsys的小的設計中,大概它的誤差在100%左右,呵呵。綜合後時間是2.9ns,布局布線和最佳化後的時間是5ns。可是ambit的綜合肯定是要比synopsys的差的,因為它沒有很大的庫的支持,在大的邏輯塊的綜合的時候我覺得就可以很明顯的感覺出來的。我沒有具體試過,那位大蝦有時間可以比較一下他們的綜合特性。

4、時序驅動的深亞微米設計

這部分是底層設計的軟體。底層設計的工作我感覺是細活,來來回回是需要走很多次重複的流程的。在以前的設計流程中( .6um及其以上 ),一般情況下對於連線延時是可以不用考慮,或是說它們對設計的影響不算很大。在設計完成後,做一下pex,然後仿真一下,小設計的話,多半是可以通過的。

很多軟體都直接在布局階段就將線路延時考慮進去,這也是深亞微米設計的要求。因為在設計中,連線延時對整體設計的影響很大,因此甚至在綜合階段就需要考慮到floorplan的影響。synopsys和ambit和jupiter(avanti!公司的綜合軟體)等在它們的綜合過程中都加入了這樣的考慮。

candence的軟體中,有se和design planner兩個主要的軟體來進行時序驅動的設計,cadence 的這塊的軟體推出很早,可惜就是更新比較慢,象avanti公司的軟體都把布局布線,時序分析和綜合等等幾乎全套的流程都統一起來的時候,cadence在底層還沒有什麼創新的地方,還是幾年前的模樣。

5、全定製ic設計工具

* virtuoso schematic composer : ic design entry 它是可以進行混合輸入的原理圖輸入方式。支持 vhdl/hdl語言的文本輸入。

* affirma analog design environment

這是一個很好的混合信號設計環境

* virtuoso layout editor版圖編輯

它支持參數化單元,應該是一個很好的特性。

* affirma spectra 高級電路仿真器

和hspice一類的。

* virtuoso layout synthesizer

直接的layout生成工具,小規模設計環境

* assura 驗證 環境,包括diva

* dracula驗證和參數提取包

* iccragtsman 布局設計的環境。在面向ip的設計中比較合適。

底層軟體

cadence 的底層軟體有下面這些:

邏輯設計規劃器

這是用於設計早期的規劃工具。其主要用途是延時預測、生成供綜合的線路負載模型。這個工具是用來在物理設計的早期象邏輯設計者提供設計的物理信息。

物理設計規劃器

物理設計的前期規劃。對於大型設計而言,物理設計的前期規劃非常重要。很多流程中,在前期的物理規劃(floorplan)結束後,就需要一次反標驗證設計的時序。

* se (silicon ensemble)布局布線器

se是一個布局布線的平台,它可以提供多個布局布線及後期處理軟體的接口。

* pbo optimization基於布局的最佳化工具

* ct-gen生成工具

* rc參數提取

hyperrules規生成,hyperextract rc提取,rc簡化,和delay計算

* pearl靜態時序分析

pearl 除了界面友好的特點外,還有就是可以和spice交換數據來進行關鍵路徑的仿真。

* vampire驗證工具

軟體管理最佳化

為了更好的管理與調度正版軟體的license問題,lanmantech公司花費五年時間從事軟體license監控管理研究,在license管控領域積累了深厚的技術經驗。其研發的lmtlicmanager軟體集中監控管理系統,可以提供全面具體的license數據統計報告、license使用分析、license自動回收釋放、license分組調度、license外借及license優先授權等功能。它的解決方案已被多家世界500強企業所採用,可以為企業節省許可證費用30%以上。

揭開面紗

全球電子設計創新領先企業cadence設計系統公司(nasdaq: cdns)推出了一種新的整體式矽實現方法,推動晶片開發超越使用點工具進行的修補方式,轉向一種流線化的、端對端式、綜合了技術、工具和方法學的方式。 和半導體和系統企業傳統上在達到矽實現過程中所採用的謹慎的、式方法相比,這種方法是一種重大突破。矽實現這一術語是指將設計變為矽片所需要的所有步驟,它是eda360行動的重要組成部分。

cadence®這種新的方法著力提供滿足三個方面要求的產品和技術,以獲得決定性的矽實現道路,這三個方面是: 統一的設計意圖、設計抽取和設計收斂。 晶片和系統製造商所面臨的最大技術和商務挑戰是:混合信號、低功耗、十億門/十億赫茲、驗證、sip和協同設計、整體效率和指標。滿足了以上三項要求的設計,能為這些製造商帶來明顯和可量化的效率、可預測性及盈利能力的提升。

隨著在整個公司的矽實現產品組合引入新技術,cadence®向前進了一大步,確保其和即將推出的產品滿足這三項關鍵的要求,並且可以納入到整體的流程中去。

就意圖而言,新的功能使模擬、物理和電氣約束能驅動數字內容到混合信號流程中,反之亦然。 提取方面,設計團隊可以為系統級封裝和立體ic設計創造出一個抽象。而對於設計收斂,cadence在、驗證和實現之間建立了新的物理、電氣和功能聯繫,在設計流程中提供了更好的收斂,縮短了eco周期。 更多詳細信息,可在此下載矽實現白皮書。

“這是我見過的cadence最好的方法,”eda首席分析師gary smith表示, “cadence不斷明確其戰略,引進人才,並使人才績效和戰略性的eda360目標掛鈎。 這樣做的目標是打破單打獨鬥的局面,使公司各部門能通力合作。 他們正在努力實現很多其他eda公司嘗試並失敗的事。”

“在當前複雜的設計和市場壓力條件下,晶片開發企業急需在效率和盈利能力方面取得重大提高,但是,僅僅把一大堆不同公司的工具拼湊在一起是不可能實現這個目標的,”cadence矽實現產品集團主管研發的高級副總裁徐季平表示。

“我們的研發團隊一直致力於建立能滿足統一設計意圖、設計抽取和設計收斂要求的工具,我們將來發布的產品還將繼續滿足這些核心要素。 最終,我們希望提供多個無縫的、端對端的設計流程,它們內在的高效率將給客戶帶來明顯的市場優勢。”

大學計畫

據悉,全球最大的eda軟體提供商cadence公司,正在積極地與國內一些著名理工科高校展開合作,以成立聯合實驗室的方式,積極推進其大學計畫。已經達成合作協定的高校包括:北京工業大學、蘇州大學、華南理工大學等(下圖為cadence中國區經理熊文、科通集團cadence產品經理王其平與華南理工大學及蘇州大學部分領導出席聯合實驗室的掛牌儀式)。 華南理工——cadence聯合實驗室

華南理工——cadence聯合實驗室

華南理工——cadence聯合實驗室

華南理工——cadence聯合實驗室cadence公司(中文名叫“鏗騰電子”或“益華電腦”)是一家世界領先的eda(電子設計自動化:electronic design automation)工具軟體公司,總部位於美國加州。其完整的產品鏈條,可服務於電子行業的全部環節,提供從ic設計到pcb設計的全流程工具支持。在世界範圍內,市場份額遙遙領先於其它競爭對手。一大批電子行業的明星企業,如蘋果、三星、惠普、戴爾、愛立信、華為……等都是cadence公司的客戶。

cadence在國際上有著高度的品牌影響力和市場份額,而中國這樣一個電子製造大國正在從中國製造朝中國設計邁進,中國市場的潛力被越來越多的國際跨國公司所重視。cadence和高校的合作,正是順應中國在設計發展的趨勢,致力於培養未來的設計人才,同時彌補早期在教育市場的不足!

在教育市場,eda工具的選擇通常帶著先入為主的性質,學生在校期間選擇某個工具進行學習的經驗,會對其以後進入工作選擇使用哪個工具產生重要影響。cadence公司在此前中國的教育市場上,顯然沒有捷足先登,而被另一個eda公司占領了較大份額。雖然在國內的大學計畫上失去了先機,但憑藉其領先的產品優勢,通過和國內一些高水平高校合作,也可以走出和其它公司的一條差異化之路。

cadence在國際上有著高度的品牌影響力和市場份額,而中國這樣一個電子製造大國正在從中國製造朝中國設計邁進,中國市場的潛力被越來越多的國際跨國公司所重視。cadence和高校的合作,正是順應中國在設計發展的趨勢,致力於培養未來的設計人才,同時彌補早期在教育市場的不足!

在教育市場,eda工具的選擇通常帶著先入為主的性質,學生在校期間選擇某個工具進行學習的經驗,會對其以後進入工作選擇使用哪個工具產生重要影響。cadence公司在此前中國的教育市場上,顯然沒有捷足先登,而被另一個eda公司占領了較大份額。雖然在國內的大學計畫上失去了先機,但憑藉其領先的產品優勢,通過和國內一些高水平高校合作,也可以走出和其它公司的一條差異化之路。

cadence對於一些高速、高密度板等高端設計有著自己獨特優勢,越是高端、複雜的設計要求,cadence的產品就越能彰顯其特點。所以,通過和國內一些具有較強科研實力的高校進行合作,共同完成一些高水平的科研項目,cadence有望在高端設計領域行使“教授母語”的優先權。從而為後期高端市場的增長和爆發進行必要的鋪墊。

不得不提的是,cadence選擇科通集團作為合作夥伴,是其市場戰略中的一個值得期待的舉措。科通集團是國內最大的元器件分銷商,納斯達克上市公司,不僅線上下業務擁有龐大的客戶資源,而且其線上業務“科通芯城”,在上線短短兩年時間,已成為國內最具影響力ic元器件電商品牌。cadence選擇科通,看中的正是科通線上線下強大的立體服務能力。同時,cadence的這次大學計畫正是在科通集團的積極推動下進行的。